18 Mar Phasing Mechanism

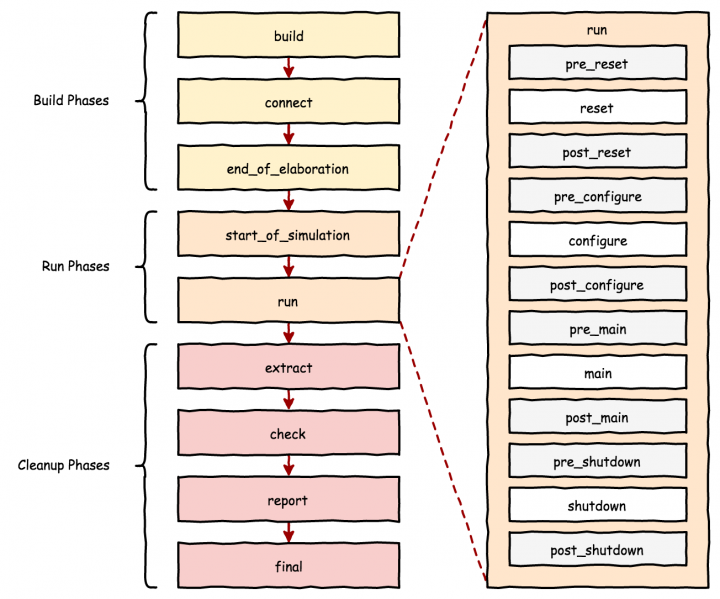

UVM testbench에서 일어나는 일은 일종의 순서를 따라 진행된다. Component가 instantiation 되어야 각 component를 연결할 수 있고, component가 서로 연결되어야 transaction을 test sequence에 따라 내보낼 수 있고, transaction이 모두 완료된 시점에서야 error 여부를 최종적으로 check 할 수 있는데, UVM은 이러한 process를 phase의 개념으로 정의하고 있다. UVM phase는 다음과 같이 크게 build phase, run phase 그리고 cleanup phase로 구분할 수 있다.

- Build phase – component를 instantiation 하고 서로 연결하는 phase

- Run phase – transaction이 오고 가는 실제 simulation이 진행되는 phase

- Cleanup phase – test의 pass/fail을 판단하고 report를 출력하는 phase

Build Phases

먼저 build_phase에서는 일반적으로 testbench를 구성하는 component를 instantiation 하고 factory에 등록하는 등의 작업을 하게 된다. Configuration database에 대한 control도 build_phase에서 많이 이루어진다.

function void build_phase(uvm_phase phase);

super.build_phase(phase);

agent = my_agent::type_id::create("agent", this);

if (!uvm_config_db#(int)::get(this, "", "my_int", my_int)) begin

my_int = -1;

end

endfunction: build_phase

connect_phase는 주로 component 간 TLM port를 연결하거나 interface를 연결하는 등의 역할을 한다.

function void connect_phase(uvm_phase phase); super.connect_phase(phase); m_driver.seq_item_port.connect(m_sequencer.seq_item_export); endfunction: connect_phase

end_of_elaboration_phase는 build phase 중 가장 마지막 phase로서 대부분의 configuration이 모두 완료되고 simulation이 시작되기 직전에 수행하고 싶은 작업을 해당 phase에 구현하게 된다.

Run Phases

start_of_simulation_phase는 simulation이 막 시작되어 시간을 consuming하기 직전 단계에 해당한다. 이 단계에서 testbench의 topology, configuration 등의 정보를 출력하기도 한다.

function void start_of_simulation_phase(uvm_phase phase); super.connect_phase(phase); uvm_top.print_topology(); endfunction: start_of_simulation_phase

run_phase는 실제 simulation에 대한 description을 하는 phase에 해당하며 시간을 consuming한다. 즉, 기타 phase와는 달리 function이 아닌 task임에 유의해야 한다. 또한 run_phase는 위 그림에 나타난 것과 같이 reset_phase, configure_phase, main_phase, shutdown_phase 등의 phase를 이용하여 필요한 경우 더욱 세부적인 phase control을 가능하게 한다. 해당 하위 phase 역시 모두 task로 이루어져 있다.

task run_phase(uvm_phase phase); super.run_phase(phase); phase.raise_objection(this); seq.start(env.agent.sequencer); phase.drop_objection(this); endtask: run_phase

Cleanup Phases

extract_phase는 simulation이 종료된 후 scoreboard와 coverage collector로부터 정보를 수집하는 등의 역할을 수행한다. check_phase는 extract_phase에서 수집한 정보를 기반으로 checking을 진행하며, report_phase는 checking의 결과를 출력한다. 마지막으로 final_phase는 추가적으로 필요한 작업을 수행하고 test를 마무리하는 단계에 해당한다.

Execution Order

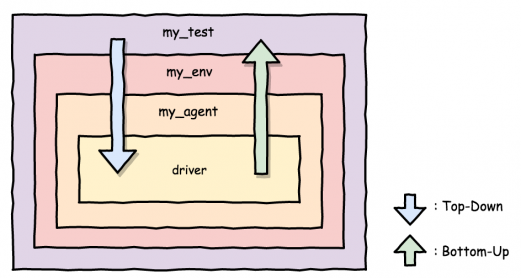

Phase에 대해서 이야기 할 때 top-down 방식과 bottom-up 방식이라는 용어에 대하여 이해할 필요가 있다. Top-down 방식이라 함은 높은 hierarchy에 있는 phase가 먼저 수행되고, 낮은 hierarchy에 있는 phase가 이후에 수행된다는 뜻이다. Bottom-up 방식은 top-down 방식과 반대 순서로 수행된다고 생각하면 된다. 아래 그림을 보면 용어의 의미를 쉽게 이해할 수 있을 것이다. UVM phase 중 build_phase와 final_phase가 top-down 방식에 해당하며, 나머지 phase는 bottom-up 방식에 해당한다. 특히 build_phase가 top-down 방식이라는 점은 기억해 두는 것이 좋다. 주로 build_phase에서 component가 instantiation 되는데, parent component가 instantiation 되지 않으면 child component가 instantiation 될 수 없기 때문에 당연히 top부터 수행되어야 함을 알 수 있다. Run phase에 해당하는 모든 phase는 예외적으로 parallel하게 수행된다.

Testbench의 component별로 각 phase 진입 시 log를 출력하면 아래와 같은 결과를 확인할 수 있다. 위에서 설명한 순서대로 각 phase가 수행되며, run_phase는 parallel하게, build_phase와 final_phase는 top-down으로, 그 외 phase는 bottom-up으로 수행되는 것도 확인 가능하다.

UVM_INFO my_test.sv(36) @ 0: uvm_test_top [my_test ] build_phase UVM_INFO my_env.sv(34) @ 0: uvm_test_top.env [my_env ] build_phase UVM_INFO my_agent.sv(37) @ 0: uvm_test_top.env.agent [my_agent ] build_phase UVM_INFO my_driver.sv(32) @ 0: uvm_test_top.env.agent.driver [my_driver] build_phase UVM_INFO my_driver.sv(40) @ 0: uvm_test_top.env.agent.driver [my_driver] connect_phase UVM_INFO my_agent.sv(49) @ 0: uvm_test_top.env.agent [my_agent ] connect_phase UVM_INFO my_env.sv(44) @ 0: uvm_test_top.env [my_env ] connect_phase UVM_INFO my_test.sv(47) @ 0: uvm_test_top [my_test ] connect_phase UVM_INFO my_driver.sv(48) @ 0: uvm_test_top.env.agent.driver [my_driver] end_of_elaboration_phase UVM_INFO my_agent.sv(57) @ 0: uvm_test_top.env.agent [my_agent ] end_of_elaboration_phase UVM_INFO my_env.sv(52) @ 0: uvm_test_top.env [my_env ] end_of_elaboration_phase UVM_INFO my_test.sv(55) @ 0: uvm_test_top [my_test ] end_of_elaboration_phase UVM_INFO my_driver.sv(56) @ 0: uvm_test_top.env.agent.driver [my_driver] start_of_simulation_phase UVM_INFO my_agent.sv(65) @ 0: uvm_test_top.env.agent [my_agent ] start_of_simulation_phase UVM_INFO my_env.sv(60) @ 0: uvm_test_top.env [my_env ] start_of_simulation_phase UVM_INFO my_test.sv(65) @ 0: uvm_test_top [my_test ] start_of_simulation_phase UVM_INFO my_env.sv(68) @ 0: uvm_test_top.env [my_env ] run_phase UVM_INFO my_agent.sv(73) @ 0: uvm_test_top.env.agent [my_agent ] run_phase UVM_INFO my_driver.sv(64) @ 0: uvm_test_top.env.agent.driver [my_driver] run_phase UVM_INFO my_test.sv(76) @ 0: uvm_test_top [my_test ] run_phase UVM_INFO my_driver.sv(72) @ 0: uvm_test_top.env.agent.driver [my_driver] extract_phase UVM_INFO my_agent.sv(81) @ 0: uvm_test_top.env.agent [my_agent ] extract_phase UVM_INFO my_env.sv(76) @ 0: uvm_test_top.env [my_env ] extract_phase UVM_INFO my_test.sv(93) @ 0: uvm_test_top [my_test ] extract_phase UVM_INFO my_driver.sv(80) @ 0: uvm_test_top.env.agent.driver [my_driver] check_phase UVM_INFO my_agent.sv(89) @ 0: uvm_test_top.env.agent [my_agent ] check_phase UVM_INFO my_env.sv(84) @ 0: uvm_test_top.env [my_env ] check_phase UVM_INFO my_test.sv(101) @ 0: uvm_test_top [my_test ] check_phase UVM_INFO my_driver.sv(88) @ 0: uvm_test_top.env.agent.driver [my_driver] report_phase UVM_INFO my_agent.sv(97) @ 0: uvm_test_top.env.agent [my_agent ] report_phase UVM_INFO my_env.sv(92) @ 0: uvm_test_top.env [my_env ] report_phase UVM_INFO my_test.sv(109) @ 0: uvm_test_top [my_test ] report_phase UVM_INFO my_test.sv(117) @ 0: uvm_test_top [my_test ] final_phase UVM_INFO my_env.sv(100) @ 0: uvm_test_top.env [my_env ] final_phase UVM_INFO my_agent.sv(105) @ 0: uvm_test_top.env.agent [my_agent ] final_phase UVM_INFO my_driver.sv(96) @ 0: uvm_test_top.env.agent.driver [my_driver] final_phase

검증 진행 중에 phase 관련하여 debugging이 필요한 경우 Command Line Processors for Debugging 페이지에 소개한 바 있는 +UVM_PHASE_TRACE 옵션 적용을 고려해 보자.

References

- http://www.verificationguide.com/p/uvm-phases.html

- http://cluelogic.com/2014/08/uvm-tutorial-for-candy-lovers-phasing/

समलैंगिक अश्लील

Posted at 15:45h, 30 Marchविंटेज अश्लील qqyyooppxx.Ptm8jJINjF9

खिलौना अश्लील बा

Posted at 23:45h, 30 Marchहेनतई, एनीमे अश्लील बा hjkvbasdfzxzz.0EJN6CNS8wN

मजेदार सेक्स पोर्न

Posted at 19:10h, 01 Aprilसेलिब्रिटी अश्लील txechdyzxca.O91mTYfztkW

मुख-मैथुन अश्लील साहित्य

Posted at 02:31h, 03 Aprilदादी अश्लील hkyonet.W9kZrlc3Zop

ladesbet ਕਮ ਸ਼ਾਟ ਪੋਰਨ

Posted at 13:38h, 05 Aprilladesbet ਹੱਥਰਸੀ ਪੋਰਨ ladesinemi.U3CQL5KHhUI

ladesbet ウェブカメラ

Posted at 15:19h, 05 Aprilladesbet シーメールポルノ ladestinemi.yrVWyI9cCE3