09 Mar Using a Variable in Properties

SystemVerilog property를 이용하여 timing specification에 대한 checker 구현 시 ##const를 이용한 delay 기술 또는 [*const]를 이용한 반복횟수 기술의 경우 반드시 constant 값이 사용되어야 한다는 제약이 있다. 즉, 상수 또는 localparam과 같이 재정의 불가능한 값을 사용하여 assertion을 기술하는 경우는 전혀 문제되지 않는다.

localparam timing = 3; // constant

property p_sva;

@(negedge clk) disable iff (!rstn)

$rose(en) |-> en[*1:timing];

endproperty: p_sva

반면 아래와 같이 int 형 변수를 사용하여 assertion을 기술하는 경우 constant 값이 사용되지 않았기 때문에 compile error가 발생하는 것을 확인할 수 있다.

int timing = 3; // variable

property p_sva;

@(negedge clk) disable iff (!rstn)

$rose(en) |-> en[*1:timing];

endproperty: p_sva

아래는 각각 Cadence Xcelium과 Synopsys VCS의 simulator 출력이다.

$rose(en) |-> en[*1:timing];

|

xmvlog: *E,NOTPAR (testbench.sv,11|31): Illegal operand for constant expression [4(IEEE)].

Error-[NCE] Non-constant expression The following expression should be a constant. Expression: timing "testbench.sv", 11 Source info: $rose(en) |-> en[*1:timing];

Local Variable in SystemVerilog Property

만약 timing parameter가 특정 조건에 의해 가변되어야 하는 경우라면 어떻게 해야 할까? module 외부에서 parameter를 이용하여 값을 입력 받아야 하거나 기타 변수들 간의 계산을 통해서 timing parameter가 결정되어야 하는 등 timing parameter를 상수 또는 localparam 등으로 constant하게 선언할 수 없는 경우가 발생할 수 있다. 아래는 이 때 적용 가능한 SVA(SystemVerilog assertion) 기술 방식을 나타낸다.

int timing = 3; // variable

property p_sva;

int t;

@(negedge clk) disable iff (!rstn)

$rose(en) |-> ##0 (1, t = timing - 1) // initialize

##1 (en, t = t - 1)[*0:$] // decrement

##1 (t <= 0); // compare

endproperty: p_sva

(1, t = timing - 1), (en, t = t - 1)과 같이 괄호 안에 쉼표로 구분하여 기술한 부분이 핵심이 된다. 괄호 안의 첫번째에 해당하는 1, en은 일반적으로 property를 작성할 때 사용되는 sequence와 동일하다고 생각하면 된다. 그 뒤에 쉼표로 구분하여 뒤따르는 t = timing - 1, t = t - 1과 같은 statement는 앞의 sequence가 참일 때 수행된다. 따라서 (1, t = timing - 1)는 $rose(en)이 high가 되는 그 시점에 무조건 t 값을 initialize 하는 역할을 하며, (en, t = t - 1)[*0:$]는 en이 high일 때 계속해서 t 값을 하나씩 decrement 하는 역할을 한다. 이후 en 값이 low가 되는 시점에 (en, t = t - 1)[*0:$]에서 빠져나오게 되며 그 다음 clock에서 t가 0보다 작거나 같으면 결과는 pass로 출력된다. 참고로 쉼표로 구분되는 문장은 하나 이상 추가될 수 있다.

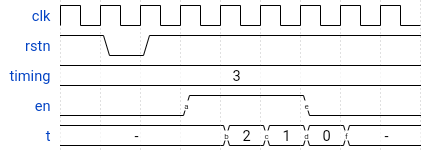

이와 같이 local variable을 활용하는 방식의 SVA는 가독성이 떨어지기 때문에 한 눈에 이해하기는 다소 어렵다. 이해를 돕기 위해 waveform과 함께 해당 waveform에 알파벳 기호로 표시된 각 node를 기준으로 동작을 추가적으로 설명한다.

- a 시점:

en신호가 rise 한다. - b-1 시점: property가

clk의 negedge에서 checking을 하므로 b 지점에서 property가 enable 된다. - b-2 시점: 동시에

en신호가 high이므로 local variable인t가timing - 1, 즉, 2의 값으로 initialize 된다. - c 시점:

en신호가 여전히 high를 유지하고 있고t는 1이 된다. - d 시점: 다시 한 번

en신호가 high를 유지하고 있으며t는 0이 된다. - e 시점:

en신호가 fall 한다. - f 시점:

en신호가 low로 변하였으므로t <= 0값을 계산하고 그 결과 참이므로 property는 pass 하게 된다.

References

No Comments