22 Mar DVCon U.S. 2018

지난 2월 26일부터 3월 1일까지 DVCon U.S. 2018이 개최되었다. Accellera가 주최하는 DVCon은 design verification 분야에서 가장 유명한 학회로 현재 검증 trend를 읽을 수 있는 많은 paper와 poster가 발표되는 큰 이벤트다. 뿐만 아니라 Cadence, Synopsys, Mentor와 같은 많은 회사에서 부스 전시도 하는 등 볼거리가 매우 많다. 위 그림을 클릭하면 DVCon 공식 웹사이트로 연결된다.

DVCon U.S.에서 발표되는 내용은 웹사이트를 통해 agenda list와 간략한 설명만을 확인할 수 있으며, 발표자료가 바로 공개되지는 않는다. 발표자료는 대략 1년이 지난 시점에 공식적으로 공개되고, 그에 따라 DVCon U.S. 2017의 발표자료가 2018년 5월 웹사이트를 통해 제공될 예정이며, DVCon U.S 2018의 발표자료는 그로부터 약 1년이 지난 후 공개될 것으로 예상된다.

개인적으로 관심 있게 보는 내용은 keynote와 best paper/poster 수상작이다. 먼저 keynote speech에서는 주로 전반적인 검증의 trend 및 challenge에 대해 이야기한다. 올 해 keynote에서는 Synopsys의 Christopher Tice가 ‘Industry’s Next Challenge: The Petacycle Challenge’를 주제로 발표하였다. 최근 automotive, IoT, 5G 등의 새로운 기술 영역이 급부상 함에 따라 검증의 요구 사항이 변하고, 그에 따라 검증 기술과 솔루션이 어떻게 변해야 하는지 다룬다.

DVCon U.S. 2018 Best Papers

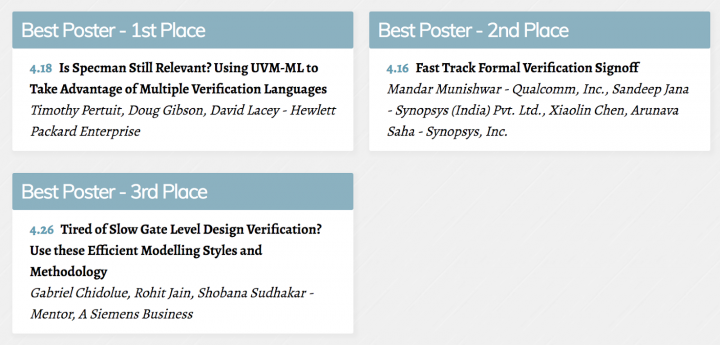

DVCon U.S. 2018 Best Posters

위에서도 언급한 것과 같이 발표자료는 현재 공식적으로 공개되지 않지만, 가끔 저자가 속한 회사 홈페이지에 발표자료가 업로드 되는 경우가 있다. DVCon U.S. 2018의 best paper 1위 자리를 차지한 ‘Is Specman Still Relevant? Using UVM-ML to Take Advantage of Multiple Verification Languages’ 발표자료도 Verilab에 의해 현재 공개되어 있다.

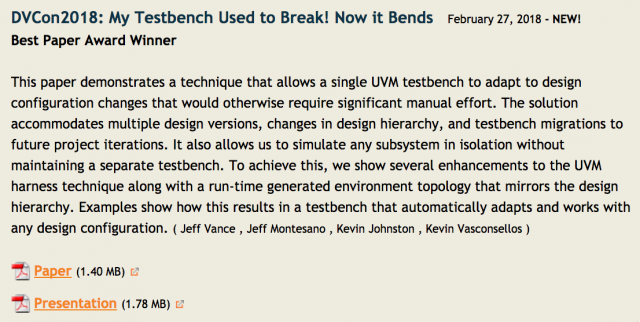

발표자료를 가볍게 훑어본 결과 현업에서 매우 유용하게 사용될 수 있을 내용이라는 느낌을 받았다. SoC를 검증할 때, SoC 전체에 대한 testbench 하나만을 가지고 검증을 완료할 수는 없다. Design의 크기가 점점 커지고 복잡해짐에 따라 여러 sub-block level에서 검증을 거친 후 전체를 묶어 검증을 진행한다. 이러한 경우 각 level별로 별도의 testbench가 필요하게 되는데, 어느 정도 common한 부분을 가지는 testbench를 여러 개 만드는 작업은 골칫거리가 되곤 한다. 뿐만 아니라 프로젝트 진행 도중 design hierarchy가 바뀌거나 여러 개의 버전의 design을 검증해야 하는 경우도 발생한다.

Verilab은 하나의 testbench로 이러한 상황을 모두 cover 할 수 있도록 여러 테크닉을 적용하였다. Verilab에서 제안하는 방법은 UVM standard인 IEEE 1800.2를 따르지만 testbench 구축 시 조금 더 strict한 guideline을 제시하는 것이다. 따라서 testbench 전체를 초기부터 직접 구축할 수 있는 경우에 의미가 있을 수 있다. 자세한 내용은 발표자료 또는 함께 제공되는 source code를 통해 확인하자.

DVCon U.S. 2018에는 항상 등장하는 UVM, coverage, formal verification, emulation 뿐만 아니라 최근 이슈가 되고 있는 PSS(Portable Stimulus Standard), safety, deep learning 등에 대해서도 다루고 있으니 꾸준히 관심을 가지고 지켜볼 필요가 있겠다.

No Comments